# From non-preemptive to preemptive scheduling using synchronization synthesis

Pavol Černý, Edmund M. Clarke, Thomas A. Henzinger, Arjun Radhakrishna, Leonid Ryzhyk, Roopsha Samanta & Thorsten Tarrach

# **Formal Methods in System Design**

An International Journal

ISSN 0925-9856

Form Methods Syst Des DOI 10.1007/s10703-016-0256-5 Volume 48, Number 3, June 2016 ISSN: 0925-9856

# FORMAL METHODS IN SYSTEM DESIGN

An International Journal

ONLIN

Special Issue: CAV 2014

Guest Editors: Armin Biere · Roderick Bloem

Your article is published under the Creative Commons Attribution license which allows users to read, copy, distribute and make derivative works, as long as the author of the original work is cited. You may selfarchive this article on your own website, an institutional repository or funder's repository and make it publicly available immediately.

# From non-preemptive to preemptive scheduling using synchronization synthesis

Pavol Černý $^1$  · Edmund M. Clarke $^2$  · Thomas A. Henzinger $^3$  · Arjun Radhakrishna $^4$  · Leonid Ryzhyk $^5$  · Roopsha Samanta $^6$  · Thorsten Tarrach $^3$

© The Author(s) 2016. This article is published with open access at Springerlink.com

**Abstract** We present a computer-aided programming approach to concurrency. The approach allows programmers to program assuming a friendly, non-preemptive scheduler, and our synthesis procedure inserts synchronization to ensure that the final program works even with a preemptive scheduler. The correctness specification is implicit, inferred from the non-preemptive behavior. Let us consider sequences of calls that the program makes to an external interface. The specification requires that any such sequence produced under

This work was published, in part, in Computer Aided Verification (CAV) 2015 [4].

Market M

Pavol Černý pavol.cerny@colorado.edu

Edmund M. Clarke emc@cs.cmu.edu

Thomas A. Henzinger tah@ist.ac.at

Arjun Radhakrishna arjunrad@cis.upenn.edu

Leonid Ryzhyk l.ryzhyk@samsung.com

Roopsha Samanta roopsha@cs.purdue.edu

Published online: 27 September 2016

- University of Colorado Boulder, 425 UCB, Boulder, CO 80309, USA

- <sup>2</sup> Carnegie Mellon University, 5000 Forbes Avenue, Pittsburgh, PA 15213, USA

- IST Austria, Am Campus 1, 3400 Klosterneuburg, Austria

- University of Pennsylvania, 3330 Walnut Street, Philadelphia, PA 19104, USA

- <sup>5</sup> Samsung Research America, 665 Clyde Avenue, Mountain View, CA 94043, USA

- 6 University of Purdue, 610 Purdue Mall, West Lafayette, IN 47907, USA

a preemptive scheduler should be included in the set of sequences produced under a non-preemptive scheduler. We guarantee that our synthesis does not introduce deadlocks and that the synchronization inserted is optimal w.r.t. a given objective function. The solution is based on a finitary abstraction, an algorithm for bounded language inclusion modulo an independence relation, and generation of a set of global constraints over synchronization placements. Each model of the global constraints set corresponds to a correctness-ensuring synchronization placement. The placement that is optimal w.r.t. the given objective function is chosen as the synchronization solution. We apply the approach to device-driver programming, where the driver threads call the software interface of the device and the API provided by the operating system. Our experiments demonstrate that our synthesis method is precise and efficient. The implicit specification helped us find one concurrency bug previously missed when model-checking using an explicit, user-provided specification. We implemented objective functions for coarse-grained and fine-grained locking and observed that different synchronization placements are produced for our experiments, favoring a minimal number of synchronization operations or maximum concurrency, respectively.

**Keywords** Synthesis · Concurrency · NFA language inclusion · MaxSAT

### 1 Introduction

Programming for a concurrent shared-memory system, such as most common computing devices today, is notoriously difficult and error-prone. Program synthesis for concurrency aims to mitigate this complexity by synthesizing synchronization code automatically [5,6,9,15]. However, specifying the programmer's intent may be a challenge in itself. Declarative mechanisms, such as assertions, suffer from the drawback that it is difficult to ensure that the specification is complete and fully captures the programmer's intent.

We propose a solution where the specification is *implicit*. We observe that a core difficulty in concurrent programming originates from the fact that the scheduler can *preempt* the execution of a thread at any time. We therefore give the developer the option to program assuming a friendly, *non-preemptive*, scheduler. Our tool automatically synthesizes synchronization code to ensure that every behavior of the program under preemptive scheduling is included in the set of behaviors produced under non-preemptive scheduling. Thus, we use the non-preemptive semantics as an implicit correctness specification.

The non-preemptive scheduling model (also known as *cooperative scheduling* [26]) can simplify the development of concurrent software, including operating system (OS) kernels, network servers, database systems, etc. [21,22]. In the non-preemptive model, a thread can only be descheduled by voluntarily yielding control, e.g., by invoking a blocking operation. Synchronization primitives may be used for communication between threads, e.g., a producer thread may use a semaphore to notify the consumer about availability of data. However, one does not need to worry about protecting accesses to shared state: a series of memory accesses executes atomically as long as the scheduled thread does not yield.

A user evaluation by Sadowski and Yi [22] demonstrated that this model makes it easier for programmers to reason about and identify defects in concurrent code. There exist alternative implicit correctness specifications for concurrent programs. For example, for functional programs one can specify the final output of the sequential execution as the correct output. The synthesizer must then generate a concurrent program that is guaranteed to produce the same output as the sequential version [3]. This approach does not allow any form of thread coordination, e.g., threads cannot be arranged in a producer–consumer fashion. In addition,

it is not applicable to reactive systems, such as device drivers, where threads are not required to terminate.

Another implicit specification technique is based on placing *atomic sections* in the source code of the program [14]. In the synthesized program the computation performed by an atomic section must appear atomic with respect to the rest of the program. Specifications based on atomic sections and specifications based on the non-preemptive scheduling model, used by our tool, can be easily expressed in terms of each other. For example, one can simulate atomic sections by placing yield statements before and after each atomic section, as well as around every instruction that does not belong to any atomic section.

We believe that, at least for systems code, specifications based on the non-preemptive scheduling model are easier to write and are less error-prone than atomic sections. Atomic sections are subject to syntactic constraints. Each section is marked by a pair of matching opening and closing statements, which in practice means that the section must start and end within the same program block. In contrast, a yield can be placed anywhere in the program.

Moreover, atomic sections restrict the use of thread synchronization primitives such as semaphores. An atomic section either executes in its entirety or not at all. In the former case, all wait conditions along the execution path through the atomic section must be simultaneously satisfied *before* the atomic section starts executing. In practice, to avoid deadlocks, one can only place a blocking instruction at the start of an atomic section. Combined with syntactic constraints discussed above, this restricts the use of thread coordination with atomic sections—a severe limitation for systems code where thread coordination is common. In contrast, synchronization primitives can be used freely under non-preemptive scheduling. Internally, they are modeled using yields: for instance, a semaphore acquisition instruction is modeled by a yield followed by an assume statement that proceeds when the semaphore becomes available.

Lastly, our specification defaults to the safe choice of assuming everything needs to be atomic unless a yield statement is placed by the programmer. In contrast, code that uses atomic sections can be preempted at any point unless protected by an explicit atomic section.

In defining behavioral equivalence between preemptive and non-preemptive executions, we focus on externally observable program behaviors: two program executions are *observationally equivalent* if they generate the same sequences of calls to interfaces of interest. This approach facilitates modular synthesis where a module's behavior is characterized in terms of its interaction with other modules. Given a multi-threaded program  $\mathscr C$  and a synthesized program  $\mathscr C'$  obtained by adding synchronization to  $\mathscr C$ ,  $\mathscr C'$  is *preemption-safe* w.r.t.  $\mathscr C$  if for each execution of  $\mathscr C'$  under a preemptive scheduler, there is an observationally equivalent non-preemptive execution of  $\mathscr C$ . Our synthesis goal is to automatically generate a preemption-safe version of the input program.

We rely on abstraction to achieve efficient synthesis of multi-threaded programs. We propose a simple, data-oblivious abstraction inspired by an analysis of synchronization patterns in OS code, which tend to be independent of data values. The abstraction tracks types of accesses (read or write) to each memory location while ignoring their values. In addition, the abstraction tracks branching choices. Calls to an external interface are modeled as writes to a special memory location, with independent interfaces modeled as separate locations. To the best of our knowledge, our proposed abstraction is yet to be explored in the verification and synthesis literature. The abstract program is denoted as  $\mathcal{C}_{abs}$ .

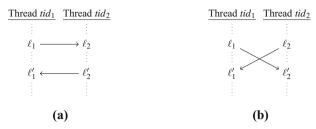

Two abstract program executions are observationally equivalent if they are equal modulo the classical independence relation I on memory accesses. This means that every sequence  $\omega$  of observable actions is equivalent to a set of sequences of observable actions that are derived from  $\omega$  by repeatedly commuting independent actions. Independent actions are

accesses to different locations, and accesses to the same location iff they are both read accesses. Using this notion of equivalence, the notion of *preemption-safety* is extended to abstract programs.

Under abstraction, we model each thread as a nondeterministic finite automaton (NFA) over a finite alphabet, with each symbol corresponding to a read or a write to a particular variable. This enables us to construct NFAs  $\mathsf{NP}_{abs}$ , representing the abstraction of the original program  $\mathscr C$  under non-preemptive scheduling, and  $\mathsf{P}_{abs}$ , representing the abstraction of the synthesized program  $\mathscr C'$  under preemptive scheduling. We show that preemption-safety of  $\mathscr C'$  w.r.t.  $\mathscr C$  is implied by preemption-safety of the abstract synthesized program  $\mathscr C'_{abs}$  w.r.t. the abstract original program  $\mathscr C_{abs}$ , which, in turn, is implied by language inclusion modulo I of NFAs  $\mathsf P_{abs}$  and  $\mathsf NP_{abs}$ . While the problem of language inclusion modulo an independence relation is undecidable [2], we show that the antichain-based algorithm for standard language inclusion [11] can be adapted to decide a bounded version of language inclusion modulo an independence relation.

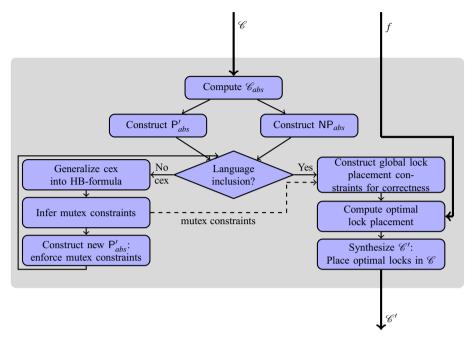

Our synthesis works in a counterexample-guided inductive synthesis (CEGIS) loop that accumulates a set of global constraints. The loop starts with a counterexample obtained from the language inclusion check. A counterexample is a sequence of locations in  $\mathcal{C}_{abs}$  such that their execution produce an observation sequence that is valid under the preemptive semantics, but not under the non-preemptive semantics. From the counterexample we infer *mutual exclusion (mutex) constraints*, which when enforced in the language inclusion check avoid returning the same counterexample again. We accumulate the mutex constraints from all counterexamples iteratively generated by the language inclusion check. Once the language inclusion check succeeds, we construct a set of global constraints using the accumulated mutex constraints and constraints for enforcing deadlock-freedom. This approach is the key difference to our previous work [4], where a greedy approach is employed that immediately places a lock to eliminate a bug. The greedy approach may result in a suboptimal lock placement with unnecessarily overlapping or nested locks.

The global approach allows us to use an objective function f to find an optimal lock placement w.r.t. f once all mutex constraints have been identified. Examples of objective functions include minimizing the number of lock statements (leading to coarse-grained locking) and maximizing concurrency (leading to fine-grained locking). We encode such an objective function, together with the global constraints, into a weighted maximum satisfiability (MaxSAT) problem, which is then solved using an off-the-shelf solver.

Since the synthesized lock placement is guaranteed not to introduce deadlocks our solution follows good programming practices with respect to locks: no double locking, no double unlocking and no locks locked at the end of the execution.

We implemented our synthesis procedure in a new prototype tool called LISS (Language Inclusion-based Synchronization Synthesis) and evaluated it on a series of device driver benchmarks, including an Ethernet driver for Linux and the synchronization skeleton of a USB-to-serial controller driver, as well as an in-memory key-value store server. First, LISS was able to detect and eliminate all but two known concurrency bugs in our examples; these included one bug that we previously missed when synthesizing from explicit specifications [6], due to a missing assertion. Second, our abstraction proved highly efficient: LISS runs an order of magnitude faster on the more complicated examples than our previous synthesis tool based on the CBMC model checker. Third, our coarse abstraction proved surprisingly precise for systems code: across all our benchmarks, we only encountered three program locations where manual abstraction refinement was needed to avoid the generation of unnecessary synchronization. Fourth, our tool finds a deadlock-free lock placement for both a fine-grained and a coarse-grained objective function. Overall, our evaluation strongly supports the use of

the implicit specification approach based on non-preemptive scheduling semantics as well as the use of the data-oblivious abstraction to achieve practical synthesis for real-world systems code. With the two objective functions we implemented, LISS produces an optimal lock placements w.r.t. the objective.

Contributions First, we propose a new specification-free approach to synchronization synthesis. Given a program written assuming a friendly, non-preemptive scheduler, we automatically generate a preemption-safe version of the program without introducing deadlocks. Second, we introduce a novel abstraction scheme and use it to reduce preemption-safety to language inclusion modulo an independence relation. Third, we present the first language inclusion-based synchronization synthesis procedure and tool for concurrent programs. Our synthesis procedure includes a new algorithm for a bounded version of our inherently undecidable language inclusion problem. Fourth, we synthesize an optimal lock placement w.r.t. an objective function. Finally, we evaluate our synthesis procedure on several examples. To the best of our knowledge, LISS is the first synthesis tool capable of handling realistic (albeit simplified) device driver code, while previous tools were evaluated on small fragments of driver code or on manually extracted synchronization skeletons.

# 2 Related work

This work is an extension of our work that appeared in CAV 2015 [4]. We included a proof for Theorem 3 that shows that language inclusion is undecidable for our particular construction of automata and independence relation. Further, we introduced a set of global mutex constraints that replace the greedy approach of our previous work and enables optimal lock placement according to an objective function.

Synthesis of synchronization is an active research area [3,5,6,8,12,15,17,23,24]. Closest to our work is a recent paper by Bloem et al. [3], which uses implicit specifications for synchronization synthesis. While their specification is given by sequential behaviors, ours is given by non-preemptive behaviors. This makes our approach applicable to scenarios where threads need to communicate explicitly. Further, correctness in Bloem et al. [3] is determined by comparing values at the end of the execution. In contrast, we compare sequences of events, which serves as a more suitable specification for infinitely-looping reactive systems. Further, Khoshnood et al. developed ConcBugAssist [18], similar to our earlier paper [15], that employs a greedy loop to fix assertion violations in concurrent programs.

Our previous work [5,6,15] develops the trace-based synthesis algorithm. The input is a program with assertions in the code, which represent an explicit correctness specification. The algorithm proceeds in a loop where in each iteration a faulty trace is obtained using an external model checker. A trace is faulty if it violates the specification. The trace is subsequently generalized to a partial order [5,6] or a formula over happens-before relations [15], both representing a set of faulty traces. A formula over happens-before relations is basically a disjunction of partial orders. In our earlier previous work [5,6] the partial order is used to synthesize atomic sections and inner-thread reorderings of independent statements. In our later work [15] the happens-before formula is used to obtain locks, wait-signal statements, and barriers. The quality of the synthesized code heavily depends on how well the generalization steps works. Intuitively the more faulty traces are removed in one synthesis step the more general the solution is and the closer it is to the solution a human would have implemented.

The drawback of assertions as a specification is that it is hard to determine if a given set of assertions represents a complete specification. The current work does not rely on an external model-checker or an explicit specification. Here we are solving language inclusion,

a computationally harder problem than reachability. However, due to our abstraction, our tool performs significantly better than tools from our previous work [5,6], which are based on a mature model checker (CBMC [10]). Our abstraction is reminiscent of previously used abstractions that track reads and writes to individual locations (e.g., [1,25]). However, our abstraction is novel as it additionally tracks some control-flow information (specifically, the branches taken) giving us higher precision with almost negligible computational cost. For the trace generalization and synthesis we use the technique from our previous work [15] to infer looks. Due to our choice of specification no other synchronization primitives are needed.

In Vechev et al. [24] the authors rely on assertions for synchronization synthesis and include iterative abstraction refinement in their framework. This is an interesting extension to pursue for our abstraction. In other related work, CFix [17] can detect and fix concurrency bugs by identifying simple bug patterns in the code.

The concepts of linearizability and serializability are very similar to our implicit specification. Linearizability [16] describes the illusion that every method of an object takes effect instantaneously at some point between the method call and return. A set of transactions is serializable [13,20] if they produce the same result, whether scheduled in parallel or in sequential order.

There has been a body of work on using a non-preemptive (cooperative) scheduler as an implicit specification. The notion of cooperability was introduced by Yi and Flanagan [26]. They require the user to annotate the program with yield statements to indicate thread interference. Then their system verifies that the yield specification is complete meaning that every trace is cooperable. A preemptive trace is cooperable if it is equivalent to a trace under the cooperative scheduler.

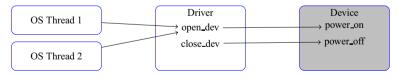

# 3 Illustrative example

Figure 2 contains our running example, a part of a device driver. A driver interfaces the operating system with the hardware device (as illustrated in Fig. 1) and may be used by different threads of the operating system in parallel. An operating system thread wishing to use the device must first call the OPEN\_DEV procedure and finally the CLOSE\_DEV procedure to indicate it no longer needs the device. The driver keeps track of the number of threads that interact with the device. The first thread to call OPEN\_DEV will cause the driver to power up

Fig. 1 Interaction of the device driver with the OS and the device

```

procedure OPEN_DEV

procedure CLOSE_DEV

if (open == 0) then

if (open > 0) then

\ell_1

\ell_5

\ell_2

POWER_UP

\ell_6

open := open - 1

\ell_7

if (open == 0) then

l3

open := open + 1

\ell_8

POWER_DOWN

\ell_4

yield

\ell_9

yield

```

Fig. 2 Running example

```

procedure OPEN_DEV_ABS

procedure CLOSE_DEV_ABS

\ell_{1a}

read(open)

\ell_{5a}

read(open)

if (*) then

if (*) then

\ell_{1b}

\ell_{5b}

la

write(dev)

\ell_{6a}

read(open)

\ell_{6b}

write(open)

\ell_{3a}

read(open)

\ell_{7a}

read(open)

\ell_{3b}

write(open)

if (*) then

\ell_{7b}

\ell_4

vield

\ell_8

write(dev)

\ell_9

yield

```

Fig. 3 Abstraction of the running example

the device, the last thread to call CLOSE\_DEV will cause the driver to power down the device. The interaction between the driver and the device are represented as procedure calls in lines  $\ell_2$  and  $\ell_8$ . From the device's perspective, the power-on and power-off signals alternate. In general, we must assume that it is not safe to send the power-on signal twice in a row to the device. If executed with the non-preemptive scheduler the code in Fig. 2 will produce a sequence of a power-on signal followed by a power-off signal followed by a power-on signal and so on.

Consider the case where the procedure OPEN\_DEV is called in parallel by two operating system threads that want to initiate usage of the device. Without additional synchronization, there could be two calls to POWER\_UP in a row when executing under a preemptive scheduler. Consider two threads (T1 and T2) running the OPEN\_DEV procedure. The corresponding trace is T1. $\ell_1$ ; T2. $\ell_1$ ; T1. $\ell_2$ ; T2. $\ell_2$ ; T2. $\ell_3$ ; T2. $\ell_4$ ; T1. $\ell_3$ ; T1. $\ell_4$ . This sequence is not observationally equivalent to any sequence that can be produced when executing with a non-preemptive scheduler.

Figure 3 contains the abstracted versions of the two procedures, OPEN\_DEV\_ABS and CLOSE DEV\_ABS. For instance, the instruction open := open +1 is abstracted to the two instructions labeled  $\ell_{3a}$  and  $\ell_{3b}$ . The calls to the device (POWER\_UP and POWER\_DOWN) are abstracted as writes to a hypothetical dev variable. This expresses the fact that interactions with the device are never independent. The abstraction is coarse, but still captures the problem. Consider two threads (T1 and T2) running the OPEN\_DEV\_ABS procedure. The following trace is possible under a preemptive scheduler, but not under a non-preemptive scheduler:  $\text{T1.}\ell_{1a}$ ;  $\mathtt{T}1.\ell_{1b};\ \mathtt{T}2.\ell_{1a};\ \mathtt{T}2.\ell_{1b};\ \mathtt{T}1.\ell_{2};\ \mathtt{T}2.\ell_{2};\ \mathtt{T}2.\ell_{3a};\ \mathtt{T}2.\ell_{3b};\ \mathtt{T}2.\ell_{4};\ \mathtt{T}1.\ell_{3a};\ \mathtt{T}1.\ell_{3b};\ \mathtt{T}1.\ell_{4}.$ Moreover, the trace cannot be transformed by swapping independent events into any trace possible under a non-preemptive scheduler. This is because instructions  $\ell_{3b}$ : write(open) and  $\ell_{1a}$ : read(open) are not independent. Further,  $\ell_2$ : write(dev) is not independent with itself. Hence, the abstract trace exhibits the problem of two successive calls to POWER\_UP when executing with a preemptive scheduler. Our synthesis procedure finds this problem, and stores it as a mutex constraint:  $mtx([\ell_{1a}:\ell_{3b}], [\ell_2:\ell_{3b}])$ . Intuitively this constraint expresses the fact if one thread is executing any instruction between  $\ell_{1a}$  and  $\ell_{3b}$  no other thread may execute  $\ell_2$  or  $\ell_{3h}$ .

While this constraint ensures two parallel calls to OPEN\_DEV behave correctly, two parallel calls to CLOSE\_DEV may result in the device receiving two POWER\_DOWN signals. This is represented by the concrete trace T1. $\ell_5$ ; T1. $\ell_6$ ; T2. $\ell_5$ ; T2. $\ell_6$ ; T2. $\ell_7$ ; T2. $\ell_8$ ; T2. $\ell_9$ ; T1. $\ell_7$ ; T1. $\ell_8$ ; T1. $\ell_9$ . The corresponding abstract trace is T1. $\ell_{5a}$ ; T1. $\ell_{5b}$ ; T1. $\ell_{6a}$ ; T1. $\ell_{6b}$ ; T2. $\ell_{5a}$ ; T2. $\ell_{5a}$ ; T2. $\ell_{6a}$ ; T2. $\ell_{6a}$ ; T2. $\ell_{7a}$ ; T2. $\ell_{7a}$ ; T2. $\ell_{7b}$ ; T2. $\ell_8$ ; T2. $\ell_9$ ; T1. $\ell_{7a}$ ; T1. $\ell_{7b}$ ; T1. $\ell_8$ ; T1. $\ell_9$ . This trace is not possible under a non-preemptive scheduler and cannot be transformed to a trace possible under a non-preemptive scheduler. This results in a second mutex constraint mtx( $\ell_{5a}$ : $\ell_8$ ,  $\ell_8$ ,  $\ell_8$ ). With both mutex constraints the program is correct. Our lock place-

```

procedure OPEN_DEV

procedure CLOSE_DEV

lock(LkVar)

lock(LkVar)

\ell_1

if (open == 0) then

\ell_5

if (open > 0) then

POWER_UP

\ell_6

open := open - 1

la

l3

open := open + 1

\ell_7

if (open == 0) then

POWER_DOWN

\ell_8

unlock(LkVar)

\ell_{\Delta}

vield

unlock(LkVar)

la

yield

```

Fig. 4 Running example with the synthesized locks

ment procedure then encodes these constraints in SMT and the models of the SMT formula are all the correct lock placements. In Fig. 4 we show OPEN\_DEV and CLOSE\_DEV with the inserted locks.

# 4 Formal framework and problem statement

We present the syntax and semantics of a *concrete* concurrent while language  $\mathcal{W}$ . For our solution strategy to be efficient we require an abstraction and we also introduce the syntax and semantics of the *abstract* concurrent while language  $\mathcal{W}_{abs}$ . While  $\mathcal{W}$  (and our tool) permits non-recursive function call and return statements, we skip these constructs in the formalization below. We conclude the section by formalizing our notion of correctness for concrete concurrent programs.

# 4.1 Concrete concurrent programs

In our work, we assume a read or a write to a single shared variable executes atomically and further assume a sequentially consistent memory model.

```

4.1.1 Syntax of W (Fig. 5)

```

A concurrent program is a finite collection of threads  $\langle T1, \ldots, Tn \rangle$  where each thread is a statement written in the syntax of  $\mathcal{W}$ . Variables in  $\mathcal{W}$  can be categorized into

- shared variables ShVar<sub>i</sub>

- thread-local variables  $LoVar_i$ ,

- lock variables LkVar<sub>i</sub>,

- condition variables *CondVar<sub>i</sub>* for wait-signal statements, and

- guard variables *GrdVar*<sub>i</sub> for assumptions.

The  $LkVar_i$ ,  $CondVar_i$  and  $GrdVar_i$  variables are also shared between all threads. All variables range over integers with the exception of guard variables that range over Booleans (true, false). Each statement is labeled with a unique location identifier  $\ell$ ; we denote by  $stmt(\ell)$  the statement labeled by  $\ell$ .

The language  $\mathcal{W}$  includes standard sequential constructs, such as assignments, loops, conditionals, and goto statements. Additional statements control the interaction between threads, such as lock, wait-notify, and yield statements. In  $\mathcal{W}$ , we only permit expressions that read from at most one shared variable and assignments that either read from or write to

exactly one shared variable. <sup>1</sup> The language also includes assume, assume\_not statements that operate on guard variables and become relevant later for our abstraction. The yield statement is in a sense an annotation as it has no effect on the actual program running under a preemptive scheduler. We still present it here because it has a semantic meaning under the non-preemptive scheduler.

Language  $\mathcal{W}$  has two statements that allow communication with an external system: input(ch) reads from and output(ch, ShExp) writes to a communication channel ch. The channel is an interface between the program and an external system. The external system cannot observe the internal state of the program and only observes the information flow on the channel. In practice, we use the channels to model device registers. A device register is a special memory address, reading and writing from and to it is visible to the device. This is used to exchange information with a device. In our presentation, we assume all channels communicate with the same external system.

# 4.1.2 Semantics of W

We first define the semantics of a single thread in  $\mathcal{W}$ , and then extend the definition to concurrent non-preemptive and preemptive semantics.

4.1.2.1 Single-thread semantics (Fig. 6) Let us fix a thread identifier tid. We use tid interchangeably with the program it represents. A state of a single thread is given by  $\langle \mathcal{V}, \ell \rangle$  where  $\mathcal{V}$  is a valuation of all program variables, and  $\ell$  is a location identifier, indicating the statement in tid to be executed next. A thread is guaranteed not to read or write thread-local variables of other threads.

We define the *flow graph*  $\mathcal{G}_{tid}$  for thread tid in a manner similar to the control-flow graph of tid. Every node of  $\mathcal{G}_{tid}$  represents a single statement (basic blocks are not merged) and the node is labeled with the location  $\ell$  of the statement. The flow graph  $\mathcal{G}_{tid}$  has a unique entry node and a unique exit node. These two may coincide if the thread has no statements. The entry node is the first labeled statement in tid; we denote its location identifier by first tid. The exit node is a special node corresponding to a hypothetical statement last tid: skip placed at the end of tid.

We define successors of locations of tid using  $\mathcal{G}_{tid}$ . The location last has no successors. We define  $succ(\ell) = \ell'$  if node  $\ell$ : stmt in  $\mathcal{G}_{tid}$  has exactly one outgoing edge to node  $\ell'$ : stmt'. Nodes representing conditionals and loops have two outgoing edges. We define  $succ_1(\ell) = \ell_1$  and  $succ_2(\ell) = \ell_2$  if node  $\ell$ : stmt in  $\mathcal{G}_{tid}$  has exactly two outgoing edges to nodes  $\ell_1$ :  $stmt_1$  and  $\ell_2$ :  $stmt_2$ . Here  $succ_1$  represents the then or the loop branch, whereas  $succ_2$  represents the else or the loopexit branch.

We can now define the single-thread operational semantics. A single execution step  $\langle \mathcal{V}, \ell \rangle \xrightarrow{\alpha} \langle \mathcal{V}', \ell' \rangle$  changes the program state from  $\langle \mathcal{V}, \ell \rangle$  to  $\langle \mathcal{V}', \ell' \rangle$ , while optionally outputting an *observable symbol*  $\alpha$ . The absence of a symbol is denoted using  $\epsilon$ . In the following, e represents an expression and  $e[v/\mathcal{V}[v]]$  evaluates an expression by replacing all variables v with their values in  $\mathcal{V}$ . We use  $\mathcal{V}[v:=k]$  to denote that variable v is set to v and all other variables in v remain unchanged.

<sup>&</sup>lt;sup>1</sup> An expression/assignment statement that involves reading from/writing to multiple shared variables can always be rewritten into a sequence of atomic read/atomic write statements using local variables. For example the statement x := x + 1, where x := x + 1 is a fresh local variable.

| LbStmt ::=                               | Labeled Statement                         |

|------------------------------------------|-------------------------------------------|

| $\ell$ : $stmt$                          | Statement annotated with a location       |

| $LbStmt_1; LbStmt_2$                     | Sequence of statements                    |

| stmt ::=                                 | Statement                                 |

| skip                                     | marks the end of the thread               |

| ShVar := LoExp                           | Assignment to shared variable             |

| LoVar := ShExp                           | Assignment to local variable              |

| ShVar := havoc                           | Assign non-deterministic value            |

| ShVar := input(ch)                       | Read a value from channel ch              |

| $output(ch,\mathit{ShExp})$              | Write value of ShExp to channel ch        |

| if $(ShExp)$ then $LbStmt_1$ else $LbSt$ | tmt <sub>2</sub> conditional              |

| while (ShExp) LbStmt                     | while loop                                |

| lock(LkVar)                              | Locks the mutex lock                      |

| $unlock(\mathit{LkVar})$                 | Unlocks the mutex lock                    |

| wait(CondVar)                            | Waits for <i>CondVar</i> to be signaled   |

| $wait\_not(CondVar)$                     | Waits for <i>CondVar</i> to be reset      |

| signal(CondVar)                          | Notifies condition variable               |

| reset(CondVar)                           | Resets condition variable                 |

| $wait\_reset(CondVar)$                   | Waits and resets in an atomic operation   |

| $assume(\mathit{GrdVar})$                | Assume guard to be true                   |

| $assume\_not(GrdVar)$                    | Assume guard to be false                  |

| $GrdVar \leftarrow GrdExpr$              | Assigns GrdVar the result of GrdExpr      |

| yield                                    | Allow current thread to be descheduled    |

| $goto(\ell)$                             | Set the instruction pointer to $\ell$     |

| LoExp ::=                                | Local-variable expression                 |

| c                                        | Integer constant                          |

| LoVar                                    | Thread-local variable                     |

| $op(LoExp_1, \ldots, LoExp_n)$           | Operator application                      |

| ShExp ::=                                | Shared-variable expression                |

| LoExp                                    | Local-variable expression                 |

| ShVar                                    | Shared variable                           |

| $op(ShVar, LoExp_1, \dots, LoExp_n)$     | Operator application with shared variable |

| GrdExpr ::=                              | Expression over guard variables           |

| ${	t true/false}$                        | Boolean constant                          |

| GrdVar                                   | Guard variable                            |

| $boolop(GrdExpr_1, \dots, GrdExpr_n)$    | Boolean operation                         |

Fig. 5 Syntax of W

In Fig. 6, we present the rules for single execution steps. Each step is atomic, no interference can occur while the expressions in the premise are being evaluated. The only rules with an observable output are:

1. HAVOC: Statement  $\ell$ : ShVar := havoc assigns shared variable ShVar a non-deterministic value (say k) and outputs the observable (tid, havoc, k, ShVar).

2. INPUT, OUTPUT:  $\ell$ : ShVar:= input(ch) and  $\ell$ : output(ch, ShExp) read and write values to the channel ch, and output (tid, in, k, ch) and (tid, out, k, ch), where k is the value read or written, respectively.

Intuitively, the observables record the sequence of non-deterministic guesses, as well as the input/output interaction with the tagged channels. The semantics of the synchronization statements shown in Fig. 6 is standard. The lock and unlock statements do not count and do not allow double (un)locking. There are no rules for goto and the sequence statement because they are already taken care of by the flow graph.

#### 4.1.3 Concurrent semantics

A state of a concurrent program is given by  $\langle \mathcal{V}, ctid, (\ell_1, \ldots, \ell_n) \rangle$  where  $\mathcal{V}$  is a valuation of all program variables, ctid is the thread identifier of the currently executing thread and  $\ell_1, \ldots, \ell_n$  are the locations of the statements to be executed next in threads  $\mathtt{T}_1$  to  $\mathtt{T}_n$ , respectively. There are two additional states:  $\langle \mathtt{terminated} \rangle$  indicates the program has finished and  $\langle \mathtt{failed} \rangle$  indicates an assumption failed. Initially, all integer program variables and ctid equal 0, all guard variable equal false and for each  $i \in [1,n]: \ell_i = \mathtt{first}_i$ . We introduce a non-preemptive and a preemptive semantics. The former is used as a specification of allowed executions, whereas the latter models concurrent sequentially consistent executions of the program.

4.1.3.1 Non-preemptive semantics (Fig. 7) The non-preemptive semantics ensures that a single thread from the program keeps executing using the single-thread semantics (Rule SEQ) until one of the following occurs: (a) the thread finishes execution (Rule THREAD\_END) or (b) it encounters a yield, lock, wait or wait\_not statement (Rule NSWITCH). In these cases, a context-switch is possible, however, the new thread must not be blocked. We consider a thread blocked if its current instruction is to acquire an unavailable lock, waits for a condition that is not signaled, or the thread reached the last location. Note the difference between wait/wait\_not and assume/assume\_not. The former allow for a context-switch while the latter transitions to the \( failed \) state if the assume is not fulfilled (rule ASSUME/ASSUME\_NOT). A special rule exists for termination (Rule TERMINATE), which requires that all threads finished execution and also all locks are unlocked.

4.1.3.2 Preemptive semantics (Figs. 7, 8) The preemptive semantics of a program is obtained from the non-preemptive semantics by relaxing the condition on context-switches, and allowing context-switches at all program points. In particular, the preemptive semantics consist of the rules of the non-preemptive semantics and the single rule PSWITCH in Fig. 8.

#### 4.2 Abstract concurrent programs

The state of the concrete semantics contains unbounded integer variables, which may result in an infinite state space. We therefore introduce a simple, data-oblivious abstraction  $\mathcal{W}_{abs}$  for concurrent programs written in  $\mathcal{W}$  communicating with an external system. The abstraction tracks types of accesses (read or write) to each memory location while abstracting away their values. Inputs/outputs to a channel are modeled as writes to a special memory location (dev). Even inputs are modeled as writes because in our applications we cannot assume that reads from the external interface are free of side-effects in the component on the other side of the interface. Havocs become ordinary writes to the variable they are assigned to. Every branch is taken non-deterministically and tracked. Given  $\mathcal{C}$  written in  $\mathcal{W}$ , we denote by  $\mathcal{C}_{abs}$  the corresponding abstract program written in  $\mathcal{W}_{abs}$ .

Fig. 6 Single-thread semantics of W

# 4.2.1 Abstract syntax (Fig. 9)

In the figure, *var* denotes all shared program variables and the dev variable. The syntax of all synchronization primitives and the assumptions over guard variables remains unchanged. The purpose of the guard variables is to improve the precision of our otherwise coarse abstraction.

```

\frac{\operatorname{ctid} = i \quad \langle \mathcal{V}, \ell_i \rangle \stackrel{\alpha}{\to} \langle \mathcal{V}', \ell_i' \rangle}{\langle \mathcal{V}, \operatorname{ctid}, (\dots, \ell_i, \dots) \rangle \stackrel{\alpha}{\to} \langle \mathcal{V}', \operatorname{ctid}, (\dots, \ell_i', \dots) \rangle} \operatorname{SEQ} }{\langle \mathcal{V}, \operatorname{ctid}, (\dots, \ell_i, \dots) \rangle \stackrel{\alpha}{\to} \langle \mathcal{V}', \operatorname{ctid}, (\dots, \ell_i', \dots) \rangle} \operatorname{Thread\_End} }   \frac{\operatorname{ctid} = i \quad \ell_i = \operatorname{last}_i \quad \operatorname{ctid}' \in \{1, \dots, n\} \quad \neg \operatorname{blocked}(\ell_{\operatorname{ctid}'}, \mathcal{V})}{\langle \mathcal{V}, \operatorname{ctid}, (\dots, \ell_i, \dots) \rangle \stackrel{\varepsilon}{\to} \langle \mathcal{V}, \operatorname{ctid}', (\dots, \ell_i, \dots) \rangle} \operatorname{Thread\_End} }   \frac{\operatorname{stmt}(\ell_i) = \operatorname{lock}(lk) / \operatorname{wait}(\operatorname{cv}) / \operatorname{wait\_not}(\operatorname{cv}) / \operatorname{wait\_reset}(\operatorname{cv}) / \operatorname{yield} }{\langle \mathcal{V}, \operatorname{ctid}, (\dots, \ell_i, \dots) \rangle \stackrel{\varepsilon}{\to} \langle \mathcal{V}, \operatorname{ctid}', (\dots, \ell_i, \dots) \rangle} \operatorname{Vi.} \ell_i = \operatorname{last}_i \quad \forall j. \, \mathcal{V}[lk_j] = 0 \\ \langle \mathcal{V}, \operatorname{ctid}, (\ell_1, \dots, \ell_n) \rangle \stackrel{\varepsilon}{\to} \langle \operatorname{terminated} \rangle \operatorname{TERMINATE}   \frac{\operatorname{ctid} = i \quad \operatorname{stmt}(\ell_i) = \operatorname{assume}(gv) / \operatorname{assume\_not}(gv) \\ \frac{\mathcal{V}[gv] = 0 / 1}{\langle \mathcal{V}, \operatorname{ctid}, (\ell_1, \dots, \ell_n) \rangle \stackrel{\varepsilon}{\to} \langle \operatorname{failed} \rangle} \operatorname{Assume\_Assume\_not}   \frac{\mathcal{V}(\operatorname{stmt}(\ell_i) = \operatorname{lock}(LkVar) \wedge \mathcal{V}[LkVar] \neq 0) \\ \vee (\operatorname{stmt}(\ell_i) = \operatorname{wait\_not}(\operatorname{CondVar}) \wedge \mathcal{V}[\operatorname{CondVar}] = 0) \\ \vee (\operatorname{stmt}(\ell_i) = \operatorname{wait\_not}(\operatorname{CondVar}) \wedge \mathcal{V}[\operatorname{CondVar}] = 1) \\ \vee (\operatorname{stmt}(\ell_i) = \operatorname{wait\_reset}(\operatorname{CondVar}) \wedge \mathcal{V}[\operatorname{CondVar}] = 0) \\ \vee (\operatorname{Stmt}(\ell_i) = \operatorname{wait\_reset}(\operatorname{CondVar}) \wedge \mathcal{V}[\operatorname{CondVar}] = 0) \\ \vee (\operatorname{Stmt}(\ell_i) = \operatorname{wait\_reset}(\operatorname{CondVar}) \wedge \mathcal{V}[\operatorname{CondVar}] = 0)

```

Fig. 7 Non-preemptive semantics

$$\frac{ctid' \in \{1, \dots, n\} \quad \neg \mathsf{blocked}(\ell_{ctid'}, \mathscr{V})}{\langle \mathscr{V}, ctid, (\ell_1, \dots, \ell_n) \rangle} \quad \mathsf{PSWITCH}$$

Fig. 8 Additional rule for preemptive semantics

Currently, they are inferred manually, but can presumably be inferred automatically using an iterative abstraction-refinement loop. In our current benchmarks, guard variables needed to be introduced in only three scenarios.

#### 4.2.2 Abstraction function (Fig. 10)

A thread in  $\mathscr{W}$  can be translated to  $\mathscr{W}_{abs}$  using the abstraction function  $\langle \rangle$ . The abstraction replaces all global variable access with  $\operatorname{read}(var)$  and  $\operatorname{write}(var)$  and replaces branching conditions with nondeterminism (\*). All synchronization primitives remain unaffected by the abstraction. The abstraction may result in duplicate labels  $\ell$ , which are replaced by fresh labels.  $\operatorname{goto}$  statements are reordered accordingly. Our abstraction records branching choices (branch tagging). If one were to remove branch-tagging, the abstraction would be unsound. The justification and intuition for this can be found further below in Theorem 1. For example in our running example in Fig. 2 the abstraction of  $\ell_1$  results in two abstract labels  $\ell_{1a}$  and  $\ell_{1b}$  in Fig. 3.

```

Variables

var ::=

ShVar

Shared variable

dev

Variable for interaction with channels

LbStmt ::=

Labeled Statement

\ell: stmt

Statement annotated with a location

LbStmt1; LbStmt2

Sequence of statements

Statement

stmt ::=

marks the end of the thread

skip

Read a shared variable var

read(var)

Write to shared variable var

write(var)

if (*) then LbStmt1 else LbStmt2

conditional

while (*) LbStmt

while loop

lock(LkVar)

Locks the mutex lock

remaining statements as in Fig. 5

```

Fig. 9 Syntax of  $\mathcal{W}_{abs}$

Fig. 10 Abstraction function from  $\mathcal{W}$  to  $\mathcal{W}_{abs}$

# 4.2.3 Abstract semantics

As before, we first define the semantics of  $\mathcal{W}_{abs}$  for a single-thread.

4.2.3.1 Single-thread semantics (Fig. 11) The abstract state of a single thread tid is given simply by  $\langle \mathcal{V}_o, \ell \rangle$  where  $\mathcal{V}_o$  is a valuation of all lock, condition and guard variables and  $\ell$  is the location of the statement in tid to be executed next. We define the flow graph and successors for locations in the abstract program tid in the same way as before. An abstract observable symbol is of the form:  $(tid, \theta, \ell)$ , where  $\theta \in \{(\text{read}, ShVar), (\text{write}, ShVar), \text{then}, \text{else}, \text{loop}, \text{exitloop}\}$ . The symbol  $\theta$  records the type of access to variables along with the variable name ((read, v), (write, v)) and records non-deterministic branching choices {if, else, loop, exitloop}. Fig. 11 presents the rules for statements unique to  $\mathcal{W}_{abs}$ ; the rules for statements common to  $\mathcal{W}_{abs}$  and  $\mathcal{W}$  are the same.

4.2.3.2 Concurrent semantics A state of an abstract concurrent program is either  $\langle \text{terminated} \rangle$ ,  $\langle \text{failed} \rangle$ , or is given by  $\langle \mathcal{V}_o, ctid, (\ell_1, \dots, \ell_n) \rangle$  where  $\mathcal{V}_o$  is a valuation of all lock, condition and guard variables, ctid is the current thread identifier and  $\ell_1, \dots, \ell_n$  are the locations of the statements to be executed next in threads  $T_1$  to  $T_n$ , respectively. The non-preemptive and preemptive semantics of a concurrent program written in  $\mathcal{W}_{abs}$  are defined in the same way as that of a concurrent program written in  $\mathcal{W}$ .

$$\frac{\operatorname{stmt}(\ell) = \operatorname{read}(var) \qquad \ell' = \operatorname{succ}(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \xrightarrow{(\operatorname{tid}, (\operatorname{read}, var), \ell)} \langle \mathcal{V}_o, \ell' \rangle} \operatorname{READ}$$

$$\frac{\operatorname{stmt}(\ell) = \operatorname{write}(var) \qquad \ell' = \operatorname{succ}(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \xrightarrow{(\operatorname{tid}, (\operatorname{write}, var), \ell)} \langle \mathcal{V}_o, \ell' \rangle} \operatorname{WRITE}$$

$$\frac{\operatorname{stmt}(\ell) = \operatorname{if}(*) \operatorname{then} \operatorname{Is}_1 \operatorname{else} \operatorname{Is}_2 \qquad \ell' = \operatorname{succ}_1(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \operatorname{If} 1$$

$$\frac{\operatorname{stmt}(\ell) = \operatorname{if}(*) \operatorname{then} \operatorname{Is}_1 \operatorname{else} \operatorname{Is}_2 \qquad \ell' = \operatorname{succ}_2(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \operatorname{If} 2$$

$$\frac{\operatorname{stmt}(\ell) = \operatorname{if}(*) \operatorname{then} \operatorname{Is}_1 \operatorname{else} \operatorname{Is}_2 \qquad \ell' = \operatorname{succ}_2(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \operatorname{If} 2$$

$$\frac{\operatorname{stmt}(\ell) = \operatorname{while}(*) \operatorname{Is} \qquad \ell' = \operatorname{succ}_1(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \xrightarrow{(\operatorname{tid}, \operatorname{loop}, \ell)} \langle \mathcal{V}_o, \ell' \rangle} \operatorname{WHILE} 1$$

$$\frac{\operatorname{stmt}(\ell) = \operatorname{while}(*) \operatorname{Is} \qquad \ell' = \operatorname{succ}_2(\ell)}{\langle \mathcal{V}_o, \ell \rangle} \xrightarrow{(\operatorname{tid}, \operatorname{exitloop}, \ell)} \langle \mathcal{V}_o, \ell' \rangle} \operatorname{WHILE} 2$$

Fig. 11 Partial set of rules for single-thread semantics of  $\mathcal{W}_{abs}$

# 4.3 Program correctness and problem statement

Let  $\mathbb{W}$ ,  $\mathbb{W}_{abs}$  denote the set of all concurrent programs in  $\mathbb{W}$ ,  $\mathbb{W}_{abs}$ , respectively.

# 4.3.1 Executions

A non-preemptive/preemptive execution of a concurrent program  $\mathscr C$  in  $\mathbb W$  is an alternating sequence of program states and (possibly empty) observable symbols,  $S_0\alpha_1S_1\ldots\alpha_kS_k$ , such that (a)  $S_0$  is the initial state of  $\mathscr C$ , (b)  $\forall j\in[0,k-1]$ , according to the non-preemptive/preemptive semantics of  $\mathscr W$ , we have  $S_j\xrightarrow{\alpha_{j+1}}S_{j+1}$ , and (c)  $S_k$  is the state  $\langle \text{terminated} \rangle$ . A non-preemptive/preemptive execution of a concurrent program  $\mathscr C_{abs}$  in  $\mathbb W_{abs}$  is defined in the same way, replacing the corresponding semantics of  $\mathscr W$  with that of  $\mathscr W_{abs}$ .

# 4.3.2 Observable behaviors

Let  $\pi$  be an execution of program  $\mathscr C$  in  $\mathbb W$ , then we denote with  $\omega = \mathsf{obs}(\pi)$  the sequence of non-empty observable symbols in  $\pi$ . We use  $[\![\mathscr C]\!]^{NP}$ , resp.  $[\![\mathscr C]\!]^P$ , to denote the *non-preemptive*, resp. *preemptive*, *observable behavior* of  $\mathscr C$ , that is all sequences  $\mathsf{obs}(\pi)$  of all executions  $\pi$  under the non-preemptive, resp. preemptive, scheduling. The *non-preemptive/preemptive observable behavior* of program  $\mathscr C_{abs}$  in  $\mathbb W_{abs}$ , denoted  $[\![\mathscr C_{abs}]\!]^P$ , is defined similarly.

We specify correctness of concurrent programs in  $\mathbb{W}$  using two *implicit* criteria, presented below.

# 4.3.3 Preemption-safety

Observable behaviors  $\omega_1$  and  $\omega_2$  of a program  $\mathscr{C}$  in  $\mathbb{W}$  are *equivalent* if: (a) the subsequences of  $\omega_1$  and  $\omega_2$  containing only symbols of the form (tid, in, k, t) and (tid, out, k, t) are equal

and (b) for each thread identifier tid, the subsequences of  $\omega_1$  and  $\omega_2$  containing only symbols of the form (tid, havoc, k, x) are equal. Intuitively, observable behaviors are equivalent if they have the same interaction with the interface, and the same non-deterministic choices in each thread. For sets  $\mathcal{O}_1$  and  $\mathcal{O}_2$  of observable behaviors, we write  $\mathcal{O}_1 \subseteq \mathcal{O}_2$  to denote that each sequence in  $\mathcal{O}_1$  has an equivalent sequence in  $\mathcal{O}_2$ .

Given concurrent programs  $\mathscr{C}$  and  $\mathscr{C}'$  in  $\mathbb{W}$  such that  $\mathscr{C}'$  is obtained by adding locks to  $\mathscr{C}$ ,  $\mathscr{C}'$  is *preemption-safe* w.r.t.  $\mathscr{C}$  if  $[\![\mathscr{C}']\!]^P \subseteq [\![\mathscr{C}]\!]^{NP}$ .

# 4.3.4 Deadlock-freedom

A state S of concurrent program  $\mathscr{C}$  in  $\mathbb{W}$  is a *deadlock state* under non-preemptive/preemptive semantics if

- (a) The repeated application of the rules of the non-preemptive/preemptive semantics from the initial state  $S_0$  of  $\mathscr{C}$  can lead to S,

- (b)  $S \neq \langle \text{terminated} \rangle$ ,

- (c)  $S \neq \langle \text{failed} \rangle$ , and

- (d)  $\neg \exists S' : \langle S \rangle \xrightarrow{\alpha} \langle S' \rangle$  according to the non-preemptive/preemptive semantics of  $\mathcal{W}$ .

Program  $\mathscr C$  in  $\mathbb W$  is deadlock-free under non-preemptive/preemptive semantics if no non-preemptive/preemptive execution of  $\mathscr C$  hits a deadlock state. In other words, every non-preemptive/preemptive execution of  $\mathscr C$  ends in state  $\langle \texttt{terminated} \rangle$  or  $\langle \texttt{failed} \rangle$ . The  $\langle \texttt{failed} \rangle$  state indicates an assumption did not hold, which we do not consider a deadlock. We say  $\mathscr C$  is deadlock-free if it is deadlock-free under both non-preemptive and preemptive semantics.

#### 4.3.5 Problem statement

We are now ready to state our main problem, the optimal synchronization synthesis problem. We assume we are given a cost function f from a program  $\mathscr{C}'$  to the cost of the lock placement solution, formally  $f: \mathbb{W} \mapsto \mathbb{R}$ . Then, given a concurrent program  $\mathscr{C}$  in  $\mathbb{W}$ , the goal is to synthesize a new concurrent program  $\mathscr{C}'$  in  $\mathbb{W}$  such that:

- (a)  $\mathscr{C}'$  is obtained by adding locks to  $\mathscr{C}$ ,

- (b)  $\mathscr{C}'$  is preemption-safe w.r.t.  $\mathscr{C}$ ,

- (c)  $\mathscr{C}'$  has no deadlocks not present in  $\mathscr{C}$ , and,

- (d)  $\mathscr{C}' = \underset{\mathscr{C}'' \in \mathbb{W} \text{ satisfying (a)-(c) above}}{\arg \min} f(\mathscr{C}'')$

# **5** Solution overview

Our solution framework (Fig. 12) consists of the following main components. We briefly describe each component below and then present them in more detail in subsequent sections.

# 5.1 Reduction of preemption-safety to language inclusion

To ensure tractability of checking preemption-safety, we build the abstract program  $\mathcal{C}_{abs}$  from  $\mathcal{C}$  using the abstraction function described in Sect. 4.2. Under abstraction, we model each thread as a nondeterministic finite automaton (NFA) over a finite alphabet consisting of

Fig. 12 Solution overview

abstract observable symbols. This enables us to construct NFAs  $NP_{abs}$  and  $P'_{abs}$  accepting the languages  $[\![\mathcal{C}_{abs}]\!]^{NP}$  and  $[\![\mathcal{C}'_{abs}]\!]^{P}$ , respectively. We proceed to check if all words of  $P'_{abs}$  are included in  $NP_{abs}$  modulo an independence relation I that respects the equivalence of observables. We describe the reduction of preemption-safety to language inclusion and our language inclusion check procedure in Sect. 6.

# 5.2 Inference of mutex constraints from generalized counterexamples

If  $\mathsf{P}'_{abs}$  and  $\mathsf{NP}_{abs}$  do not satisfy language inclusion modulo I, then we obtain a counterexample cex. A counterexample is a sequence of locations an observation sequence that is in  $[\![\mathcal{C}_{abs}]\!]^P$ , but not in  $[\![\mathcal{C}'_{abs}]\!]^{NP}$ . We analyze cex to infer constraints on  $\mathcal{L}(\mathsf{P}'_{abs})$  for eliminating cex. We use nhood(cex) to denote the set of all permutations of the symbols in cex that are accepted by  $\mathsf{P}'_{abs}$ . Our counterexample analysis examines the set nhood(cex) to obtain an nhood(cex) a Boolean combination of nhood(cex). Thus nhood(cex) is generalized into a larger set of counterexamples represented as nhood(cex). Thus nhood(cex) is generalized into a larger set of counterexamples represented as nhood(cex). We infer possible nhood(cex) that can eliminate all counterexamples satisfying nhood(cex). We describe the procedure for finding constraints from nhood(cex) in Sect. 7.1.

#### 5.3 Automaton modification for enforcing mutex constraints

Once we have the mutex constraints inferred from a generalized counterexample, we enforce them in  $P'_{abs}$ , effectively removing transitions from the automaton that violate the mutex constraint. This completes our loop and we repeat the language inclusion check of  $P'_{abs}$  and  $NP_{abs}$ . If another counterexample is found our loop continues, if the language inclusion check

succeeds we proceed to the lock placement. This differs from the greedy approach employed in our previous work [4] that modifies  $\mathscr{C}'_{abs}$  and then constructs a new automaton  $\mathsf{P}'_{abs}$  from  $\mathscr{C}'_{abs}$  before restarting the language inclusion. The greedy approach inserts locks into  $\mathscr{C}'_{abs}$  that are never removed in a future iteration. This can lead to inefficient lock placement. For example a larger lock may be placed that completely surrounds an earlier placed lock.

# 5.4 Computation of an f-optimal lock placement

Once  $\mathsf{P}'_{abs}$  and  $\mathsf{NP}_{abs}$  satisfy language inclusion modulo I, we formulate global constraints over lock placements for ensuring correctness. These global constraints include all mutex constraints inferred over all iterations and constraints for enforcing deadlock-freedom. Any model of the global constraints corresponds to a lock placement that ensures program correctness. We describe the formulation of these global constraints in Sect. 8.

Given a cost function f, we compute a lock placement that satisfies the global constraints and is optimal w.r.t. f. We then synthesize the final output  $\mathscr{C}'$  by inserting the computed lock placement in  $\mathscr{C}$ . We present various objective functions and describe the computation of their respective optimal solutions in Sect. 9.

# 6 Checking preemption-safety

# 6.1 Reduction of preemption-safety to language inclusion

# 6.1.1 Soundness of the abstraction

Formally, two observable behaviors  $\omega_1 = \alpha_0 \dots \alpha_k$  and  $\omega_2 = \beta_0 \dots \beta_k$  of an abstract program  $\mathscr{C}_{abs}$  in  $\mathbb{W}_{abs}$  are *equivalent* if:

- (A1) For each thread tid, the subsequences of  $\alpha_0 \dots \alpha_k$  and  $\beta_0 \dots \beta_k$  containing only symbols of the form  $(tid, a, \ell)$ , for all a, are equal,

- (A2) For each variable var, the subsequences of  $\alpha_0 \dots \alpha_k$  and  $\beta_0 \dots \beta_k$  containing only write symbols (of the form  $(tid, (write, var), \ell)$ ) are equal, and

- (A3) For each variable var, the multisets of symbols of the form  $(tid, (read, var), \ell)$  between any two write symbols, as well as before the first write symbol and after the last write symbol are identical.

Using this notion of equivalence, the notion of preemption-safety is extended to abstract programs: Given abstract concurrent programs  $\mathscr{C}_{abs}$  and  $\mathscr{C}'_{abs}$  in  $\mathbb{W}_{abs}$  such that  $\mathscr{C}'_{abs}$  is obtained by adding locks to  $\mathscr{C}_{abs}$ ,  $\mathscr{C}'_{abs}$  is *preemption-safe* w.r.t.  $\mathscr{C}_{abs}$  if  $\llbracket \mathscr{C}'_{abs} \rrbracket^P \subseteq_{abs} \rrbracket \mathscr{C}_{abs} \rrbracket^{NP}$ .

For the abstraction to be sound we require only that whenever preemption-safety does not hold for a program  $\mathscr{C}$ , then there must be a trace in its abstraction  $\mathscr{C}_{abs}$  feasible under preemptive, but not under non-preemptive semantics.

To illustrate this we use the program in Fig. 13, which is not preemption-safe. To see this consider the observation (T1, out, 10, ch) that cannot occur in the non-preemptive semantics because x is always 0 at  $\ell_4$ . Note that  $\ell_3$  is unreachable because the variable y is initialized to 0 and never assigned. With the preemptive semantics the output can be observed if thread T2 interrupts thread T1 between lines  $\ell_1$  and  $\ell_4$ . An example trace would be  $\ell_1$ ;  $\ell_6$ ;  $\ell_2$ ;  $\ell_4$ ;  $\ell_5$ .

If we consider the abstract semantics, we notice that under the non-preemptive abstract semantics  $\ell_3$  is reachable because the abstraction makes the branching condition in  $\ell_2$  non-deterministic. However, since our abstraction is sound there must still be an obser-

**Fig. 13** Example showing how the abstraction works

| x := 0; y := 0          |                   |

|-------------------------|-------------------|

| Thread T1               | Thread T2         |

| $\ell_1$ x := 0         | $\ell_6 \ x := 1$ |

| $\ell_2$ if (y) then    |                   |

| $\ell_3$ yield          |                   |

| $\ell_4$ if (x) then    |                   |

| $\ell_5$ output(ch, 10) |                   |

|                         |                   |

vation sequence that is observable under the abstract preemptive semantics, but not under the abstract non-preemptive semantics. This observation sequence is  $(T1, (write, x), \ell_1)$ ,  $(T2, (write, x), \ell_6)$ ,  $(T1, (read, y), \ell_2)$ ,  $(T1, else, \ell_2)$ ,  $(T1, (read, x), \ell_4)$ ,  $(T1, then, \ell_2)$ ,  $(T1, (write, dev), \ell_5)$ . The branch tagging records that the else branch is taken in  $\ell_2$ . The non-preemptive semantics cannot produce this observation sequences because it must also take the else branch in  $\ell_2$  and can therefore not reach the yield statement and context-switch. As a site note, it is also not possible to transform this observation sequence into an equivalent one under the non-preemptive semantics because of the write to x at  $\ell_6$  and the accesses to x in  $\ell_1$  and  $\ell_4$ .

This example illustrates why branch tagging is crucial to soundness of the abstraction. If we assume a hypothetical abstract semantics without branch tagging we would get the following preemptive observation sequence: (T1, (write, x),  $\ell_1$ ), (T2, (write, x),  $\ell_6$ ), (T1, (read, y),  $\ell_2$ ), (T1, (read, x),  $\ell_4$ ), (T1, (write, dev),  $\ell_5$ ). This sequence would also be a valid observation sequence under the non-preemptive semantics, because it could take the then branch in  $\ell_2$  and reach the yield statement and context-switch.

**Theorem 1** (soundness) Given concurrent program  $\mathscr{C}$  and a synthesized program  $\mathscr{C}'$  obtained by adding locks to  $\mathscr{C}$ ,  $\llbracket \mathscr{C}'_{abs} \rrbracket^P \subseteq_{abs} \llbracket \mathscr{C}_{abs} \rrbracket^{NP} \Longrightarrow \llbracket \mathscr{C}' \rrbracket^P \subseteq \llbracket \mathscr{C} \rrbracket^{NP}$ .

*Proof* It is easier to prove the contrapositive:  $[\![\mathscr{C}']\!]^P \notin [\![\mathscr{C}]\!]^{NP} \implies [\![\mathscr{C}_{abs}]\!]^P \notin_{abs}$  $[\![\mathscr{C}_{abs}]\!]^{NP}$ .

$[\![\mathscr{C}']\!]^P \notin [\![\mathscr{C}]\!]^{NP}$  means that there is an observation sequence  $\omega'$  of  $[\![\mathscr{C}']\!]^P$  with no equivalent observation sequence in  $[\![\mathscr{C}]\!]^{NP}$ . We now show that the abstract sequence  $\omega'_{abs}$  in  $[\![\mathscr{C}'_{abs}]\!]^P$  corresponding to the sequence  $\omega'$  has no equivalent sequence in  $[\![\mathscr{C}_{abs}]\!]^{NP}$ .

Towards contradiction we assume there is such an equivalent sequence  $\omega_{abs}$  in  $[\![C_{abs}]\!]^{NP}$ . We show that if  $\omega_{abs}$  indeed existed it would correspond to a concrete sequence  $\omega$  that is equivalent to  $\omega'$ , thereby contradicting our assumption.

By (A1)  $\omega_{abs}$  would have the same control flow as  $\omega'_{abs}$  because of the branch tagging. By (A2) and (A3)  $\omega_{abs}$  would have the same data-flow, meaning all reads from global variables are reading the values written by the same writes as in  $\omega'_{abs}$ . Since all interactions with the environment are abstracted to Write(dev) the order of interactions must be the same between  $\omega_{abs}$  and  $\omega'_{abs}$ . This means that, assuming all inputs and havoes are returning the same value, in the execution  $\omega$  corresponding to  $\omega_{abs}$  all variables valuation are identical to those in  $\omega'$ . Therefore,  $\omega$  is feasible and its interaction with the environment is identical to  $\omega'$  as all variable valuations are identical. Identical interaction with the environment is how equivalence between  $\omega$  and  $\omega'$  is defined. This concludes our proof.

# 6.1.2 Language inclusion modulo an independence relation

We define the problem of language inclusion modulo an independence relation. Let I be a non-reflexive, symmetric binary relation over an alphabet  $\Sigma$ . We refer to I as the *independence*

relation and to elements of I as independent symbol pairs. We define a symmetric binary relation  $\approx_I$  over words in  $\Sigma^*$ : for all words  $\sigma$ ,  $\sigma' \in \Sigma^*$  and  $(\alpha, \beta) \in I$ ,  $(\sigma \cdot \alpha \beta \cdot \sigma', \sigma \cdot \beta \alpha \cdot \sigma') \in \approx_I$ . Let  $\approx_I^t$  denote the reflexive transitive closure of  $\approx_I$ . Given a language  $\mathscr L$  over  $\Sigma$ , the closure of  $\mathscr L$  w.r.t. I, denoted  $\text{Clo}_I(\mathscr L)$ , is the set  $\{\sigma \in \Sigma^* : \exists \sigma' \in \mathscr L \text{ with } (\sigma, \sigma') \in \mathscr L$ . Thus,  $\text{Clo}_I(\mathscr L)$  consists of all words that can be obtained from some word in  $\mathscr L$  by repeatedly commuting adjacent independent symbol pairs from I.

**Definition 1** (Language inclusion modulo an independence relation) Given NFAs A, B over a common alphabet  $\Sigma$  and an independence relation I over  $\Sigma$ , the language inclusion problem modulo I is:  $\mathcal{L}(A) \subseteq \text{Clo}_I(\mathcal{L}(B))$ ?

# 6.1.3 Data independence relation

We define the data independence relation  $I_D$  over our observable symbols. Two symbols  $\alpha = (tid_{\alpha}, a_{\alpha}, \ell_{\alpha})$  and  $\beta = (tid_{\beta}, a_{\beta}, \ell_{\beta})$  are independent,  $(\alpha, \beta) \in I_D$ , iff (I0)  $tid_{\alpha} \neq tid_{\beta}$  and one of the following hold:

- (I1)  $a_{\alpha}$  or  $a_{\beta}$  in {then, else, loop, loopexit}

- (I2)  $a_{\alpha}$  and  $a_{\beta}$  are both (read, var)

- (I3)  $a_{\alpha}$  is in {(write,  $var_{\alpha}$ ), (read,  $var_{\alpha}$ )} and  $a_{\beta}$  is in {(write,  $var_{\beta}$ ), (read,  $var_{\beta}$ )} and  $var_{\alpha} \neq var_{\beta}$

# 6.1.4 Checking preemption-safety

Under abstraction, we model each thread as a nondeterministic finite automaton (NFA) over a finite alphabet consisting of abstract observable symbols. This enables us to construct NFAs NP<sub>abs</sub> and P'<sub>abs</sub> accepting the languages  $[\mathcal{C}_{abs}]^{NP}$  and  $[\mathcal{C}'_{abs}]^{P}$ , respectively.  $\mathcal{C}_{abs}$  is the abstract program corresponding to the input program  $\mathcal{C}$  and  $\mathcal{C}'_{abs}$  is the program corresponding to the result of the synthesis  $\mathcal{C}'$ . It turns out that preemption-safety of  $\mathcal{C}'$  w.r.t.  $\mathcal{C}$  is implied by preemption-safety of  $\mathcal{C}'_{abs}$  w.r.t.  $\mathcal{C}_{abs}$ , which, in turn, is implied by language inclusion modulo  $I_D$  of NFAs  $P'_{abs}$  and NP<sub>abs</sub>. NFAs  $P'_{abs}$  and NP<sub>abs</sub> satisfy language inclusion modulo  $I_D$  if any word accepted by  $P'_{abs}$  is equivalent to some word obtainable by repeatedly commuting adjacent independent symbol pairs in a word accepted by NP<sub>abs</sub>.

**Proposition 1** Given concurrent programs  $\mathscr{C}$  and  $\mathscr{C}'$ ,  $[\![\mathscr{C}'_{abs}]\!]^P \in_{abs} [\![\mathscr{C}_{abs}]\!]^{NP}$  iff  $\mathscr{L}(\mathsf{P}'_{abs}) \subseteq \mathsf{Clo}_{I_D}(\mathscr{L}(\mathsf{NP}_{abs}))$ .

*Proof* By construction  $\mathsf{P}'_{abs}$ , resp.  $\mathsf{NP}_{abs}$ , accept exactly the observation sequences that  $\mathscr{C}'_{abs}$ , resp.  $\mathscr{C}_{abs}$ , may produce under the preemptive, resp. non-preemptive, semantics (denoted by  $[\![\mathscr{C}'_{abs}]\!]^P$ , resp.  $[\![\mathscr{C}_{abs}]\!]^{NP}$ ). It remains to show that two observation sequences  $\omega_1 = \alpha_0 \dots \alpha_k$  and  $\omega_2 = \beta_0 \dots \beta_k$  are equivalent iff  $\omega_1 \in \mathsf{Clo}_{I_D}(\{\omega_2\})$ .

We first show that  $\omega_1 \in \operatorname{Clo}_{I_D}(\{\omega_2\})$  implies  $\omega_1$  is equivalent to  $\omega_2$ . The proof proceeds by induction: The base case is that no symbols are swapped and is trivially true. The inductive case assumes that  $\omega'$  is equivalent to  $\omega_2$  and we needs to show that after one single swap operation in  $\omega'$ , resulting in  $\omega''$ ,  $\omega'$  is equivalent to  $\omega''$  and therefore by transitivity also equivalent to  $\omega_2$ . Rule (AI) holds because  $I_D$  does not allow symbols of the same thread to be swapped (I0). To prove (A2) we use the fact that writes to the same variable cannot be

$<sup>^2</sup>$  The equivalence classes of  $\approx^t_I$  are Mazurkiewicz traces.

```

Thread T2

Thread T1

\ell_1 while (*) do

\ell_{12} simA \leftarrow true

signal(ch-sym)

⊳ choose symbol

\ell_{13} simA \leftarrow false

wait_reset(ch-sym-compl)

\ell_3

\mathtt{s}\mathtt{A}^1 \leftarrow \Delta^1_\mathtt{A}(\mathtt{s}\mathtt{A}^1,\ldots,\mathtt{s}\mathtt{A}^n,\tau^1,\ldots,\tau^p)

\ell_{4}

Thread T_{\alpha}

\ell_5

\ell_{14} while (*) do

\begin{array}{l} \mathtt{s}\mathtt{A}^n \leftarrow \varDelta_A^n(\mathtt{s}\mathtt{A}^1, \dots, \mathtt{s}\mathtt{A}^n, \tau^1, \dots, \tau^p) \\ \mathtt{s}\mathtt{B}^1 \leftarrow \varDelta_B^1(\mathtt{s}\mathtt{B}^1, \dots, \mathtt{s}\mathtt{B}^m, \tau^1, \dots, \tau^p) \end{array}

\ell_{15}

wait_reset(ch-sym)

\tau^1 \leftarrow \alpha^1

\ell_{16}

\ell_8

\ell_{17}

\mathtt{s} \mathtt{B}^m \leftarrow \Delta^m_R(\mathtt{s} \mathtt{B}^1, \dots, \mathtt{s} \mathtt{B}^m, \tau^1, \dots, \tau^p)

\tau^p \leftarrow \alpha^p

\ell_{18}

\ell_{10} final \leftarrow (simA \Longrightarrow

write(v_{\{\alpha,\alpha_1\}})

\ell_{o1}

\bigvee_{q \in F_A} (\mathtt{s}\mathtt{A}^1 = q^1 \wedge \dots \wedge \mathtt{s}\mathtt{A}^n = q^n))

\wedge \left( \neg \mathtt{simA} \Longrightarrow \bigvee_{q \in F_B} (\mathtt{sB}^1 = q^1 \wedge \dots \wedge \mathtt{sB}^m = q^m) \right)

\ell_{ok}

\mathsf{write}(v_{\{\alpha,\alpha_{k}\}})

\ell_{19}

signal(ch-sym-compl)

\ell_{11} assume(final)

```

Fig. 14 Simulator algorithm

swapped (I2), (I3). To prove (A3) we use the fact that reads and writes to the same variable are not independent (I2), (I3).

It remains to show that  $\omega_1$  is equivalent to  $\omega_2$  implies  $\omega_1 \in \operatorname{Clo}_{I_D}(\{\omega_2\})$ . Clearly  $\omega_1$  and  $\omega_2$  consist of the same multiset of symbols (AI). Therefore it is possible to transform  $\omega_2$  into  $\omega_1$  by swapping adjacent symbols. It remains to show that all swaps involve independent symbols. By (AI) the order of events in each thread does not change, therefore condition (I0) is always fulfilled. Branch tags can swap with every other symbol (II) and accesses to different variables can swap with each other (I3). For each variables ShVar (A2) ensures that writes are in the same order and (A3) allows reads in between to be reordered. These swaps are allowed by (I2). No other swaps can occur.

# 6.2 Checking language inclusion

We first focus on the problem of language inclusion modulo an independence relation (Definition 1). This question corresponds to preemption-safety (Theorem 1, Proposition 1) and its solution drives our synchronization synthesis.

**Theorem 2** For NFAs A, B over alphabet  $\Sigma$  and a symmetric, irreflexive independence relation  $I \subseteq \Sigma \times \Sigma$ , the problem  $\mathcal{L}(A) \subseteq \text{Clo}_I(\mathcal{L}(B))$  is undecidable [2].

We now show that this general undecidability result extends to our specific NFAs and independence relation  $I_D$ .

**Theorem 3** For NFAs  $\mathsf{P}'_{abs}$  and  $\mathsf{NP}_{abs}$  constructed from  $\mathscr{C}_{abs}$ , the problem  $\mathscr{L}(\mathsf{P}'_{abs}) \subseteq \mathsf{Clo}_{I_D}(\mathscr{L}(\mathsf{NP}_{abs}))$  is undecidable.

*Proof* Our proof is by reduction from the language inclusion modulo an independence relation problem (Definition 1). Theorem 3 follows from the undecidability of this problem (Theorem 2).

Assume we are given NFAs  $A = (Q_A, \Sigma, \Delta_A, Q_{t,A}, F_A)$  and  $B = (Q_B, \Sigma, \Delta_B, Q_{t,B}, F_B)$  and an independence relation  $I \subseteq \Sigma \times \Sigma$ . Without loss of generality we assume A and

B to be deterministic, complete, and free of  $\epsilon$ -transitions, meaning from every state there is exactly one transition for each symbol. We show that we can construct a program  $\mathscr{C}_{abs}$  that is preemption-safe iff  $\mathscr{L}(A) \subseteq \operatorname{Clo}_I(\mathscr{L}(B))$ .

For our reduction we construct a program  $\mathscr{C}_{abs}$  that simulates A or B if run with a preemptive scheduler and simulates only B if run with a non-preemptive scheduler. Note that  $\mathscr{L}(A) \cup \mathscr{L}(B) \subseteq \operatorname{Clo}_I(\mathscr{L}(B))$  iff  $\mathscr{L}(A) \subseteq \operatorname{Clo}_I(\mathscr{L}(B))$ . For every symbol  $\alpha \in \Sigma$  our simulator produces a sequence  $\omega_{\alpha}$  of abstract observable symbols. We say two such sequences  $\omega_{\alpha}$  and  $\omega_{\beta}$  commute if  $\omega_{\alpha} \cdot \omega_{\beta} \approx^t_{I_D} \omega_{\beta} \cdot \omega_{\alpha}$ , i.e, if  $\omega_{\beta} \cdot \omega_{\alpha}$  can be obtained from  $\omega_{\alpha} \cdot \omega_{\beta}$  by repeatedly swapping adjacent symbol pairs in  $I_D$ .

We will show that (a)  $\mathscr{C}_{abs}$  simulates A or B if run with a preemptive scheduler and simulates only B if run with a non-preemptive scheduler, and (b) sequences  $\omega_{\alpha}$  and  $\omega_{\beta}$  commute iff  $(\alpha, \beta) \in I$ .

The simulator is shown in Fig. 14. States and symbols of A and B are mapped to natural numbers and represented as bitvectors to enable simulation using the language  $\mathcal{W}_{abs}$ . In particular we use Boolean guard variables from  $\mathcal{W}_{abs}$  to represent the bitvectors. We use true to represent 1 and false to represent 0. As the state space and the alphabet are finite we know the number of bits needed a priori. We use n, m, and p for the number of bits needed to represent  $Q_A$ ,  $Q_B$ , and  $\Sigma$ , respectively. The transition functions  $\Delta_A$  and  $\Delta_B$  likewise work on the individual bits. We represent bitvector x of length p as  $x^1 \dots x^n$ .

Thread T1 simulates both automata A and B simultaneously. We assume the initial states of A and B are mapped to the number 0. In each iteration of the loop in thread T1 a symbol  $\alpha \in \Sigma$  is chosen non-deterministically and applied to both automata (we discuss this step in the next paragraph). Whether thread T1 simulates A or B is decided only in the end: depending on the value of simA we assert that a final state of A or B was reached. The value of simA is assigned in thread T2 and can only be true if T2 is preempted between locations  $\ell_{12}$  and  $\ell_{13}$ . With the non-preemptive scheduler the variable simA will always be false because thread T2 cannot be preempted. The simulator can only reach the  $\langle terminated \rangle$  state if all assumptions hold as otherwise it would end in the  $\langle failed \rangle$  state. The guard final will only be assigned true in  $\ell_{10}$  if either simA is false and a final state of B has been reached or if simA is true and a final state of A has been reached. Therefore the valid non-preemptive executions can only simulate B. In the preemptive setting the simulator can simulate either A or B because simA can be either true or false. Note that the statement in location  $\ell_{10}$  executes atomically and the value of simA cannot change during its evaluation. This means that  $P'_{abs}$  simulates  $\mathcal{L}(A) \cup \mathcal{L}(B)$  and  $NP_{abs}$  simulates  $\mathcal{L}(B)$ .

We use  $\tau$  to store the symbol used by the transition function. The choice of the next symbol needs to be non-deterministic to enable simulation of A, B and there is no havoc statement in  $\mathscr{W}_{abs}$ . We therefore use the fact that the next thread to execute is chosen non-deterministically at a preemption point. We define a thread  $\mathbb{T}_{\alpha}$  for every  $\alpha \in \Sigma$  that assigns to  $\tau$  the number  $\alpha$  maps to. Threads  $\mathbb{T}_{\alpha}$  can only run if the conditional variable  $\mathtt{ch-sym}$  is set to 1 by the notify statement in  $\ell_2$ . The wait\_reset(ch-sym-comp1) in  $\ell_3$  is a preemption point for the non-preemptive semantics. Then, exactly one thread  $\mathbb{T}_{\alpha}$  can proceed because the wait\_reset(ch-sym) statement in  $\ell_{15}$  atomically resets ch-sym to 0. After setting  $\tau$  and outputting the representation of  $\alpha$  thread  $\mathbb{T}_{\alpha}$ , notifies thread  $\mathbb{T}_1$  using condition variable ch-sym-comp1. Another symbol can only be produced in the next loop iteration of  $\mathbb{T}_1$ .

To produce an observable sequence faithful to I for each symbol in  $\Sigma$  we define a homomorphism h that maps symbols from  $\Sigma$  to sequences of observables. Assuming the symbol  $\alpha \in \Sigma$  is chosen, we produce the following observables: